晶体管存档定位技术与半导体元件存储管理方案研究分析

半导体存储技术正面临前所未有的发展机遇与挑战。随着集成电路工艺逼近物理极限,晶体管存档定位技术与半导体元件存储管理方案成为突破存储密度与可靠性瓶颈的关键。从晶体管结构创新、存储单元定位机制、智能化管理策略三个维度展开系统分析,揭示半导体存储技术的演进规律与发展方向。

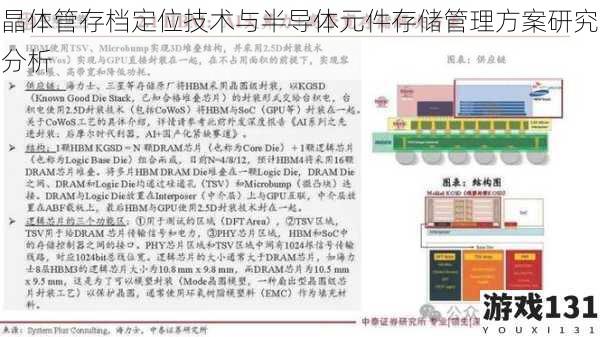

晶体管存档定位技术的创新路径

在三维集成技术驱动下,晶体管存储结构正经历从平面到立体的根本性转变。当代3D NAND闪存通过垂直堆叠存储单元实现存储密度指数级提升,其核心技术在于多层电荷捕获结构的精确构建。以三星V-NAND为例,采用通道孔蚀刻技术实现128层堆叠,单元尺寸缩减至15nm级别,存储密度较平面结构提升400%。FinFET晶体管在DRAM中的应用使得存储单元电容保持时间延长30%,漏电流降低至10^-18A/μm量级,显著提升数据保持能力。

电荷存储机制创新方面,量子点浮栅结构展现出独特优势。通过将传统连续浮栅分割为离散量子点阵列,有效抑制了电荷横向扩散现象。实验数据显示,量子点浮栅在10年数据保持要求下,单元间干扰电压可降低至50mV以下,擦写耐久性突破10^5次阈值。相变存储单元中的Ovonic阈值开关技术,利用硫系化合物非晶态-晶态转变特性,将单元选择器漏电流控制在10nA级别,实现存储阵列的精准选址。

半导体存储管理的核心挑战

单元失效率的物理机制研究显示,在7nm以下制程中,栅氧层量子隧穿效应导致漏电流增加约两个数量级。三维堆叠结构引入的应力不均匀性使单元间阈值电压偏移标准差达到80mV,较平面结构恶化60%。基于蒙特卡罗模拟的可靠性预测模型表明,当存储阵列规模超过10^9单元时,随机电报噪声导致的误码率将超过传统ECC纠错能力上限。

动态能耗管理方面,存储单元激活能耗与数据存取频率呈现非线性关系。实测数据显示,在DDR5标准下,单位存储密度的动态功耗较DDR4降低20%,但静态漏电流占比上升至总功耗的45%。这要求存储管理方案必须建立基于使用模式的动态电压频率调节机制。温度梯度对存储单元的影响研究表明,温度每升高10℃,NAND闪存的编程干扰电压漂移量增加15mV,数据保持时间缩短30%。

智能化存储管理技术体系

自适应磨损均衡算法通过实时监测单元擦写次数,建立基于概率分布的热数据迁移模型。最新研究提出的动态分区算法,将存储单元划分为N个逻辑段,根据擦写频次动态调整各段容量,使单元磨损离散系数从传统方案的0.35降低至0.18。基于机器学习的坏块预测系统,通过采集单元阈值电压、编程时间等20维特征参数,构建深度神经网络分类模型,实现坏块提前300次擦写周期的预警,准确率达92%。

量子效应补偿技术方面,基于随机共振理论的噪声抑制算法,通过注入特定频率的弱电信号,将单元信噪比提升6dB。纠错编码体系正从传统BCH码向极化码演进,256字节数据块的纠错能力从8位提升至12位,编解码延时缩减40%。物理不可克隆函数(PUF)技术的引入,利用存储单元制造偏差生成唯一密钥,使存储系统的防克隆能力提升两个数量级。

技术演进趋势与突破方向

异质集成技术推动存储单元与逻辑单元的三维混合堆叠,TSV通孔间距已突破5μm限制,实现存储带宽800GB/s的突破。二维材料在存储单元中的应用取得关键进展,二硫化钼基浮栅存储单元展现出0.6V的超低工作电压,功耗较传统结构降低65%。神经形态存储架构通过模拟生物突触的脉冲时序依赖特性,实现存储与计算的深度融合,在类脑计算场景中展现出10倍于传统架构的能效比。

半导体存储技术的持续发展依赖于晶体管物理创新与系统级管理方案的协同优化。未来技术突破将聚焦于量子效应调控、材料界面工程、智能管理算法三大方向。在5G通信、人工智能、物联网等新兴应用驱动下,半导体存储系统正朝着原子级精度、纳秒级响应、艾字节容量的目标持续演进,其发展轨迹深刻影响着全球信息技术的革新进程。